# V2V EDTECH LLP

Online Coaching at an Affordable Price.

## **OUR SERVICES:**

- Diploma in All Branches, All Subjects

- Degree in All Branches, All Subjects

- BSCIT/CS

- Professional Courses

- +91 93260 50669

- **► V2V EdTech LLP**

- w2vedtech.com

- o v2vedtech

**WINTER – 19EXAMINATION**

**Model Answer**

Subject Code:

22423

#### **Important Instructions to examiners:**

**Subject Name: Linear Integrated Circuit**

- 1) The answers should be examined by key words and not as word-to-word as given in themodel answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may tryto assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given moreImportance (Not applicable for subject English and Communication Skills.

- 4) While assessing figures, examiner may give credit for principal components indicated in thefigure. The figures drawn by candidate and model answer may vary. The examiner may give credit for anyequivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constantvalues may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

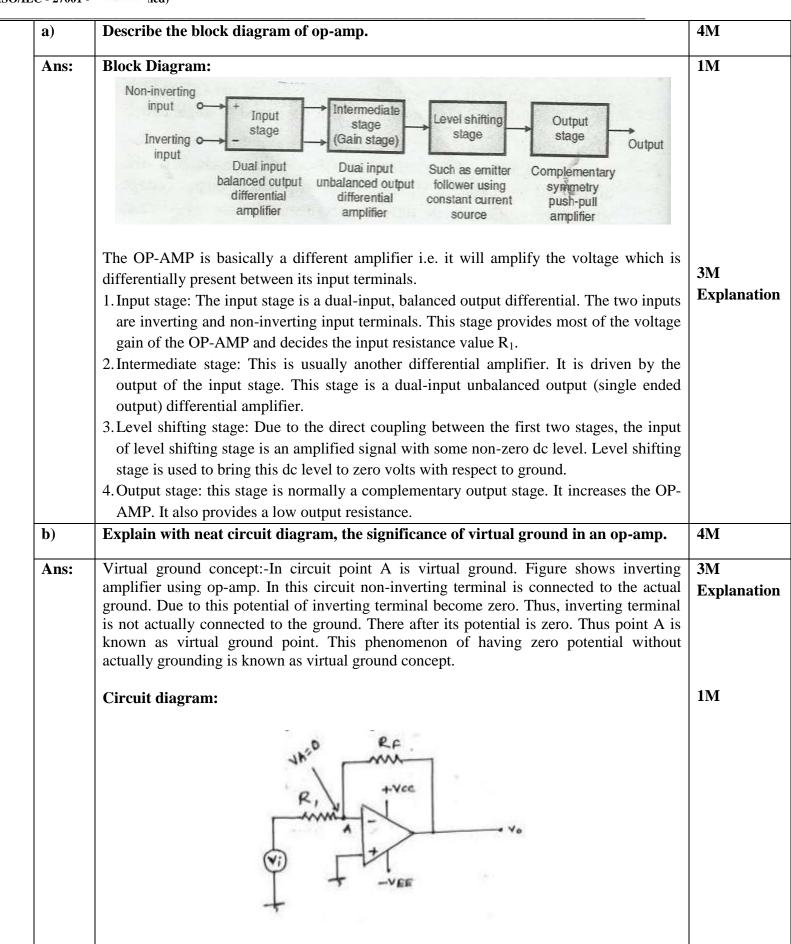

| Q.<br>No. | Sub<br>Q. N. | Answer                                                                                                                   | Marking<br>Scheme |

|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------|-------------------|

| Q.1       |              | Attempt any FIVE of the following:                                                                                       | 10-Total<br>Marks |

|           |              | Define the operational amplifier parameters.                                                                             | 2M                |

|           | <b>a</b> )   | i)Slew rate                                                                                                              |                   |

|           |              | ii) Input bias current                                                                                                   |                   |

|           | Ans:         | i) Slew Rate: it is defined as the maximum rate of change of o/p voltage per unit time & its                             | 1M                |

|           |              | $0.5 \text{ per volt/use } [S.R=\infty].$                                                                                | Each              |

|           |              | ii) Input Bias Current: Input Bias Current is the average of the currents entering into the                              |                   |

|           |              | positive & negative terminals of an op-Amp & its value is 200 nA                                                         |                   |

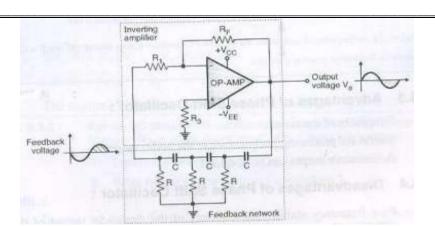

|           | <b>b</b> )   | Draw Wien bridge oscillator circuit using IC 741.                                                                        | 2M                |

|           | Ans:         | $ \begin{array}{c c} \hline  & R_1(R_4) & B & R_F(R_3) \\ \hline  & OP-AMP & V_0 \end{array} $ $ f = \frac{1}{2\pi RC} $ | 2M                |

|           | c)           | List four specifications of IC LM324.                                                                                    | 2M                |

#### MAHARASHTRA (Autonomous) (ISO/IEC - 27001 -

## )ARD OF TECHNICAL EDUCATION

| Ans:       | 1. Integrated with four Op-Amps in a single package                                                | ½ M   |

|------------|----------------------------------------------------------------------------------------------------|-------|

|            | 2. Wide power supply Range                                                                         | Each  |

|            | i) Singe supply – 3V to 32V                                                                        |       |

|            | ii) Dual supply $-\pm 1.5$ V to $\pm 16$ V                                                         |       |

|            | 3. Low Supply current – 700uA                                                                      |       |

|            | 4. Single supply for four op-amp operation enables reliable operation                              |       |

|            | 5. Operating ambient temperature – 0°C to 70°C                                                     |       |

|            | 6. Soldering pin temperature – 260 °C (for 10 seconds – prescribed)                                |       |

| <b>d</b> ) | State the four applications of an instrumentation amplifier.                                       | 2M    |

| Ans:       | The instrumentation amplifier can be used for other application such as                            | ½ M   |

|            | 1. Electronic weighing machine scale                                                               | Each  |

|            | 2 .Light, intensity meter                                                                          | Zucii |

|            | 3. Pressure monitoring & controlling                                                               |       |

|            | 4. Temperature monitoring and controlling.                                                         |       |

|            | 5. Process Instrumentation in measurement of physical quantities.                                  |       |

| e)         | State the four advantages of active filter over passive filter.                                    | 2M    |

| Ans:       | Advantages of active filter over passive filter:                                                   | ½ M   |

| Alis.      | 1. Gain and frequency adjustment flexibility since the op-amp is able to providing                 |       |

|            | gain; the input signal is not attenuated as in case of passive filters.                            | Each  |

|            | 2. Active filter is easier to tune or adjust as compare to passive filters.                        |       |

|            | 3. No loading problem because active filter provides excellent isolation between                   |       |

|            | individual stages due to high input impedance.                                                     |       |

|            | 4. Active filters are small in size and less bulky (due to absence of "L") and rugged.             |       |

|            | 5. Non floating input and output.                                                                  |       |

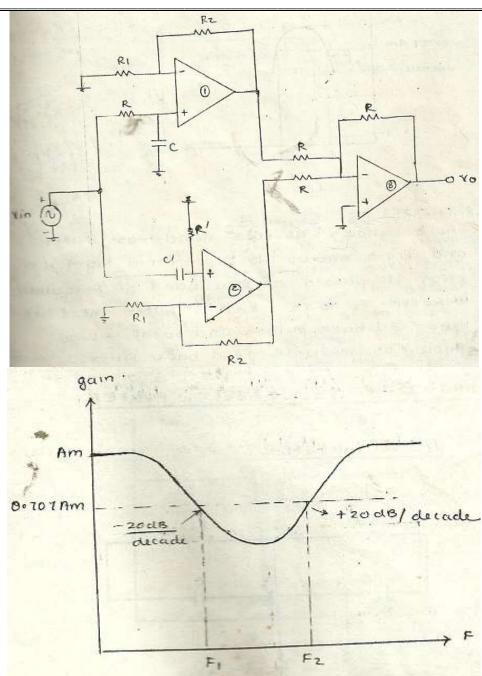

| <b>f</b> ) | Define roll of rate and order of filter.                                                           | 2M    |

| Ans:       | 1. Roll of rate is the rate of change of gain with frequency. Roll of rate is always measured in   | 2M    |

| Alls:      | dB/decade.                                                                                         | 2111  |

|            | 2. The roll of rate is called the order of the filter.                                             |       |

|            | It depends on the rate at which filter's gain changes with frequency.                              |       |

|            | For example:                                                                                       |       |

|            | •                                                                                                  |       |

|            | i) If roll off rate is -20 dB / decade or +20 dB / decade then the filter is of 1st order.         |       |

|            | ii) If roll of rate is-40 dB / decade or +40 db / decade then the filter is of 2nd order and so on |       |

| <b>g</b> ) | State the function of following pins of IC 555                                                     | 2M    |

| 8)         | i) Threshhold                                                                                      |       |

|            | ii) Discharge                                                                                      |       |

| Ans:       | i) Threshhold voltage- When positive going pulse is applied at this pin but it is more             | 2M    |

|            | positive than reference voltage (2/3vce) of upper comparator. Hence, o/p of upper                  |       |

|            | comparator becomes high i.e. S=0, R=1. Due to this, flip-flop becomes reset that's why             |       |

|            | $\bar{Q}$ =1 which goes to base of NPN transistor is ON & the external capacitor ct starts         |       |

|            | discharging to transistor to words zero. At the same time, the o/p of timer goes low.              |       |

|            | ii) Discharge- The external capacitor Ct is connected at this pin and capacitor discharge          |       |

|            | through this pin                                                                                   | 1     |

| Q.2 | Attempt any THREE of the following: | 12-Total<br>Marks |

|-----|-------------------------------------|-------------------|

|     |                                     | 1.111.115         |

| c)   | Draw the circuit diagram of grounded load type V to I converter and derive expression for its output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>4M</b> |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Ans: | Diagram:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2M        |

|      | • The analysis of the circuit can be done by following two steps: First step is to determine the voltage $V_1$ at the non-inverting (+) terminal and the second step is to establish relationship between $V_1$ and the load current $I_L$ .  • Applying KCL at node $V_3$ , $I_1 = I_1 + I_2$ (1)  But $I_1 = V_{in} - V_1 / R$ and $I_2 = V_{or} V_1 / R$ . Substituting these expression into equation (1) $I_L = \frac{V_{in} - V_1}{R} + \frac{V_o - V_1}{R}$ $\therefore V_{in} + V_o - 2 V_1 = I_L R$ $\therefore V_1 = \frac{V_{in} + V_o - I_L R}{2}$ ass we have obtained the expression for V1. | 2M        |

| <b>a</b> ) | Describe the basic integrator circuit using op-amp.                                                                                                                                                                            | 4M                                   |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Ans:       | The basic operational amplifier integrator circuit consists of an op amp with a capacitor between the output and the inverting input, and a resistor from the inverting input to the overall circuit input as shown in figure. | 2M<br>explanatio<br>with<br>equation |

|            | Vin A -Vout                                                                                                                                                                                                                    | 1M for<br>Diagram                    |

|            | Equation for output of integrator as shown below where input is Vin and Rin input resistance and C is capacitor                                                                                                                |                                      |

|            | $V_{out} = -\frac{1}{R_{in}C}\int_0^t V_{in} dt = -\int_0^t V_{in} \frac{dt}{R_{in}.C}$                                                                                                                                        |                                      |

|            | By equation it is understood that output is proportional integration of input voltage.  Output of given input signal as shown below.                                                                                           |                                      |

|            | Input Signal   Output Signal                                                                                                                                                                                                   |                                      |

|            | Square Wave Spikes                                                                                                                                                                                                             | 1M for an<br>one outpu<br>waveform   |

|            | Triangular Wave Rectangular                                                                                                                                                                                                    |                                      |

|            | Sine Wave Cosine Sine                                                                                                                                                                                                          |                                      |

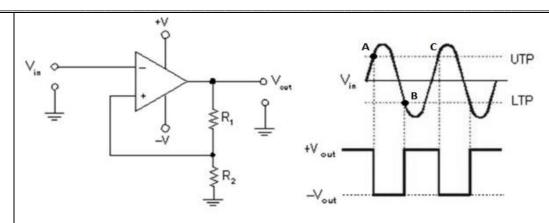

| <b>b</b> ) | Compare comparator and Schmitt trigger circuit (any four points).                                                                                                                                                              | 4M                                   |

| Ans:       |                                                                                                                                                                                                                                | 1M                                   |

|            | Sr. Parameter Comparator Schmitt Trigger                                                                                                                                                                                       | each any<br>point                    |

|            | 1 Feedback Absent i.e. open loop Present i.e. closed loop                                                                                                                                                                      |                                      |

|            | 2 Hysteresis Absent Present                                                                                                                                                                                                    | 1                                    |

|            | 3                                 | Number of reference                                                                               | One                                                                                    | TWO (UTP and LTP)                                                                                                             |                                                   |

|------------|-----------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

|            | 4                                 | Application                                                                                       | Zero crossing detector, Level detector                                                 | Sine wave to Square wave generator, pulse counter                                                                             |                                                   |

|            | 5                                 | Definition                                                                                        | Comparator compare two signal one is called reference and other is called input signal | Schmitt trigger is inverting comparator with positive feedback                                                                |                                                   |

|            | 6                                 | Noise<br>Margin                                                                                   | Low                                                                                    | More                                                                                                                          |                                                   |

|            | 7                                 | Level                                                                                             | single                                                                                 | Double                                                                                                                        |                                                   |

|            | 8                                 | Diagram                                                                                           | Non-inverting input  V  Inverting input  Negative power supply  Negative power supply  | V <sub>ie</sub> $\Diamond$ |                                                   |

| <b>c</b> ) |                                   | n a first order l<br>sume C=0.01µl                                                                | <br> low pass filter at a cut off frequen<br> F)                                       | ncy 12KHz with pass band gain                                                                                                 | 4M                                                |

| Ans:       | $F_h = 1$ $A_f=1$ $2=1$ $R_2/R_1$ | 2Khz ,A <sub>f</sub> =2<br>+ R <sub>f</sub> / R <sub>1</sub><br>+ R <sub>f</sub> / R <sub>1</sub> |                                                                                        |                                                                                                                               | 2 M<br>Resistor<br>feedbac<br>( 1M for<br>formula |

|            | 12K=<br>R=1/2                     | /2πRC<br>1/2πRC<br>2πX 12KX.01μF<br>326 KΩ Actual                                                 | l value (1.2 KΩ)                                                                       |                                                                                                                               | 2M for<br>Resistor<br>cut off<br>frequen          |

|            | Circu                             | nit Diagram:                                                                                      | Low Pass Filter Stage  R =1.2kequencies  high frequencies                              |                                                                                                                               | 1 for<br>formula                                  |

|            |                                   | Vin                                                                                               | .01uF R1 10K Rf=                                                                       | Vout<br>10K                                                                                                                   |                                                   |

|            |                                   |                                                                                                   | <b>+</b>                                                                               |                                                                                                                               |                                                   |

Ans: Diagram: -2M diagram · Vec Circuit A voltage controlled oscillator is an oscillator whose frequency is controlled by an input 2Mvoltage. Basically, the voltage input into the VCO controls how many times a digital explanation signal will oscillate in a given time period. It is basically astable multivibrator configuration in which pin 5 is connected to variable voltage terminal in which square wave generator which output frequency can vary by varying voltage at pin 5. OR + Vcc 555 Timing Capacitor Voltage Waveform Circuit Voltage Controlled Oscillator Pin 5 terminal is voltage control terminal and its function is to control the threshold and trigger levels. Normally, the control voltage is ++2/3V<sub>CC</sub> because of the internal voltage divider. However, an external voltage can be applied to this terminal directly or through a pot, as illustrated in figure, and by adjusting the pot, control voltage can be varied. Voltage across the timing capacitor is depicted in figure, which varies between +V<sub>control</sub> and ½ V<sub>control</sub>. If control voltage is increased, the capacitor takes a longer to charge and discharge; the frequency, therefore, decreases. Thus the fre-quency can be changed by changing the control volt-age. 12-Total **Q.4** Attempt any THREE of the following: Marks a) **4M** Compare open loop and closed loop configuration of operational

|            | amplifie     | r(any four poi                     | ints)                                                                                                                                  |                                                                                            |                   |

|------------|--------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------|

| Ans:       | Sr. No       | Parameter                          | Open Loop Configuration                                                                                                                | Closed loop configuration                                                                  | 4M                |

|            |              |                                    |                                                                                                                                        | 1 0                                                                                        |                   |

|            | 1            | Feedback                           | Absent                                                                                                                                 | Present                                                                                    |                   |

|            | 2            | Voltage<br>Gain                    | High ideally infinite                                                                                                                  | Low                                                                                        |                   |

|            | 3            | Gain<br>control                    | Not possible                                                                                                                           | possible                                                                                   |                   |

|            | 4            | Input<br>Resistance                | No change or Cannot Control                                                                                                            | Can Control by adjusting feedback component                                                |                   |

|            | 5            | Output<br>Resistance               | No change or Cannot Control                                                                                                            | Can Control by adjusting feedback component                                                |                   |

|            | 6            | Bandwidth                          | No change or Cannot Control                                                                                                            | Can Control by adjusting feedback component                                                |                   |

|            | 7            | Offset<br>voltage                  | No change or Cannot Control                                                                                                            | Can Control by adjusting feedback component                                                |                   |

|            | 8            | Application                        | Comparator                                                                                                                             | All application circuit such as amplifier, oscillator, filter, adder subtract or and so on |                   |

|            | 9            | Stability                          | unstable                                                                                                                               | stable                                                                                     |                   |

| <b>b</b> ) |              | he circuit diag<br>on for its gain | ram of closed loop non-invertin                                                                                                        | ng amplifier and derive                                                                    | 4M                |

| Ans:       | Diagran      | 1:                                 | I <sub>1</sub> V <sub>p</sub> | +V <sub>5</sub>                                                                            | 2 M               |

|            | Where Vn=Vi= | Vn is node volt                    | oncept $V_n = V_p = V_i$ age at inverting terminal and $V_i$ is                                                                        | s input voltage                                                                            | 2M<br>Explanation |

|            | Since no current is flow between inverting and non inverting terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|            | $I_1=I_2=I$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

|            | Vi=R1X I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |

|            | $Vo=Rf X I + R_1 XI$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |

|            | Voltage Gain= Vo/ Vi = $(Rf X I + R_1XI)/ R1X I$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |

|            | $= \frac{(Rf + R1)}{R1}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |

|            | = 1 + Rf/R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

| <u>c)</u>  | Explain the working of PLL as multiplier using block diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4M           |

| Ange       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2M           |

| Ans:       | Diagram:-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21 <b>V1</b> |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |

|            | Input Phase Amplifier LPF VCO fout = Nfin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |

|            | Detector Ampunet 1 cm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |

|            | tin Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |

|            | 565 PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |

|            | Divide by N network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

|            | fout/N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |

|            | 75,75 T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |

|            | A frequency multiplier can be designed using a PLL and a 'divided by N' counter. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2M           |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2M           |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2M           |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2M           |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the output of the counter fn. hence fin=fn= (fout )/N                                                                                                                                                                                                                                                                                                                                                                                                       | 2M           |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the output of the counter fn. hence fin=fn= (fout )/N where foutis the <u>VCO</u> output frequency,                                                                                                                                                                                                                                                                                                                                                         | 2M           |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the output of the counter fn. hence fin=fn= (fout )/N where fout is the $\underline{VCO}$ output frequency, Therefore, fout =NX fin.                                                                                                                                                                                                                                                                                                                        | 2M           |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the output of the counter fn. hence fin=fn= (fout )/N where foutis the VCO output frequency, Therefore, fout =NX fin.  Thus when the system is in lock, the VCO is actually running at the multiple of input                                                                                                                                                                                                                                                | 2M           |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the output of the counter fn. hence fin=fn= (fout )/N where foutis the VCO output frequency, Therefore, fout =NX fin.  Thus when the system is in lock, the VCO is actually running at the multiple of input frequency. The desired amount of multiplication can be obtained by selecting a proper                                                                                                                                                          | 2M           |

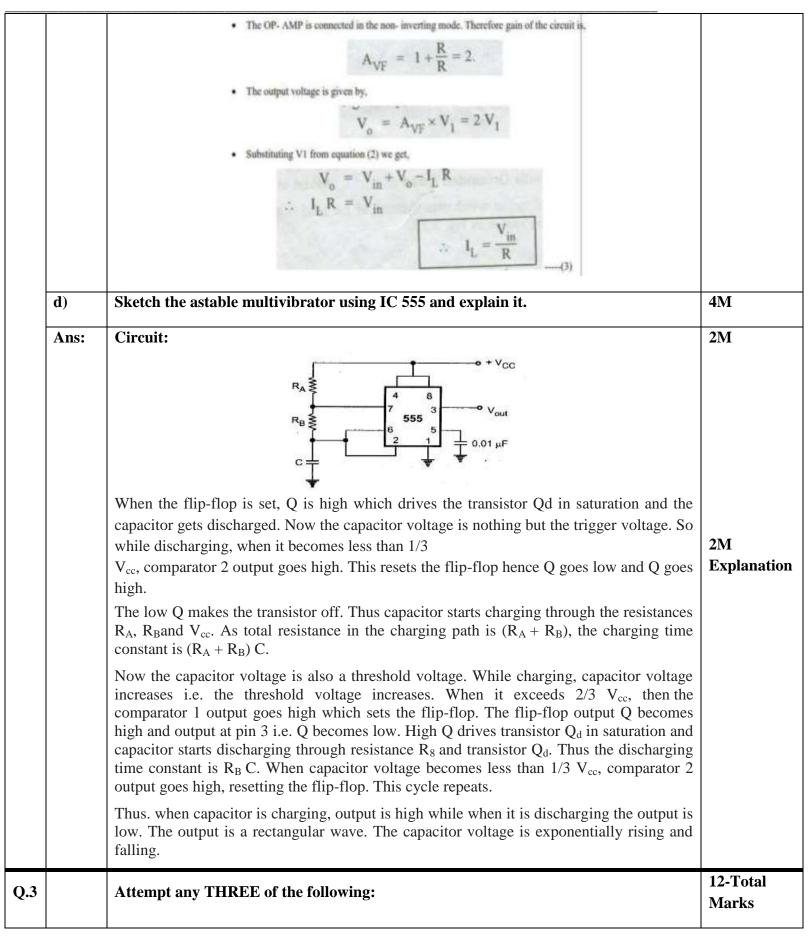

| <b>d</b> ) | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the output of the counter fn. hence fin=fn= (fout )/N where foutis the VCO output frequency, Therefore, fout =NX fin.  Thus when the system is in lock, the VCO is actually running at the multiple of input frequency. The desired amount of multiplication can be obtained by selecting a proper divide by N network, where N is an integer.                                                                                                              |              |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the output of the counter fn. hence fin=fn= (fout )/N where foutis the VCO output frequency, Therefore, fout =NX fin.  Thus when the system is in lock, the VCO is actually running at the multiple of input frequency. The desired amount of multiplication can be obtained by selecting a proper                                                                                                                                                          | 4M           |

| d)<br>Ans: | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the output of the counter fn. hence fin=fn= (fout )/N where foutis the VCO output frequency, Therefore, fout =NX fin.  Thus when the system is in lock, the VCO is actually running at the multiple of input frequency. The desired amount of multiplication can be obtained by selecting a proper divide by N network, where N is an integer.  Draw the neat circuit diagram of first order high pass filter and explain its                               |              |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the output of the counter fn. hence fin=fn= (fout )/N where foutis the VCO output frequency, Therefore, fout =NX fin.  Thus when the system is in lock, the VCO is actually running at the multiple of input frequency. The desired amount of multiplication can be obtained by selecting a proper divide by N network, where N is an integer.  Draw the neat circuit diagram of first order high pass filter and explain its                               | 4M           |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the output of the counter fn. hence fin=fn= (fout )/N where foutis the VCO output frequency, Therefore, fout =NX fin.  Thus when the system is in lock, the VCO is actually running at the multiple of input frequency. The desired amount of multiplication can be obtained by selecting a proper divide by N network, where N is an integer.  Draw the neat circuit diagram of first order high pass filter and explain its operation.                    | 4M           |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the output of the counter fn. hence fin=fn= (fout )/N where foutis the VCO output frequency, Therefore, fout =NX fin.  Thus when the system is in lock, the VCO is actually running at the multiple of input frequency. The desired amount of multiplication can be obtained by selecting a proper divide by N network, where N is an integer.  Draw the neat circuit diagram of first order high pass filter and explain its operation.                    | 4M           |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the output of the counter fn. hence fin=fn= (fout )/N where fout is the VCO output frequency, Therefore, fout =NX fin.  Thus when the system is in lock, the VCO is actually running at the multiple of input frequency. The desired amount of multiplication can be obtained by selecting a proper divide by N network, where N is an integer.  Draw the neat circuit diagram of first order high pass filter and explain its operation.  Inverting filter | 4M           |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the output of the counter fn. hence fin=fn= (fout )/N where foutis the VCO output frequency, Therefore, fout =NX fin.  Thus when the system is in lock, the VCO is actually running at the multiple of input frequency. The desired amount of multiplication can be obtained by selecting a proper divide by N network, where N is an integer.  Draw the neat circuit diagram of first order high pass filter and explain its operation.                    | 4M           |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the output of the counter fn. hence fin=fn= (fout )/N where fout is the VCO output frequency, Therefore, fout =NX fin.  Thus when the system is in lock, the VCO is actually running at the multiple of input frequency. The desired amount of multiplication can be obtained by selecting a proper divide by N network, where N is an integer.  Draw the neat circuit diagram of first order high pass filter and explain its operation.  Inverting filter | 4M           |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the output of the counter fn. hence fin=fn= (fout )/N where fout is the VCO output frequency, Therefore, fout =NX fin.  Thus when the system is in lock, the VCO is actually running at the multiple of input frequency. The desired amount of multiplication can be obtained by selecting a proper divide by N network, where N is an integer.  Draw the neat circuit diagram of first order high pass filter and explain its operation.  Inverting filter | 4M           |

|            | frequency divider is inserted between the VCO and phase detector of PLL circuit. Therefore, one input of the phase comparator is the input signal and the other is the output of 'divided by N' counter. when the lock is established the input frequency fin equals the output of the counter fn. hence fin=fn= (fout )/N where fout is the VCO output frequency, Therefore, fout =NX fin.  Thus when the system is in lock, the VCO is actually running at the multiple of input frequency. The desired amount of multiplication can be obtained by selecting a proper divide by N network, where N is an integer.  Draw the neat circuit diagram of first order high pass filter and explain its operation.  Inverting filter | 4M           |

### )ARD OF TECHNICAL EDUCATION

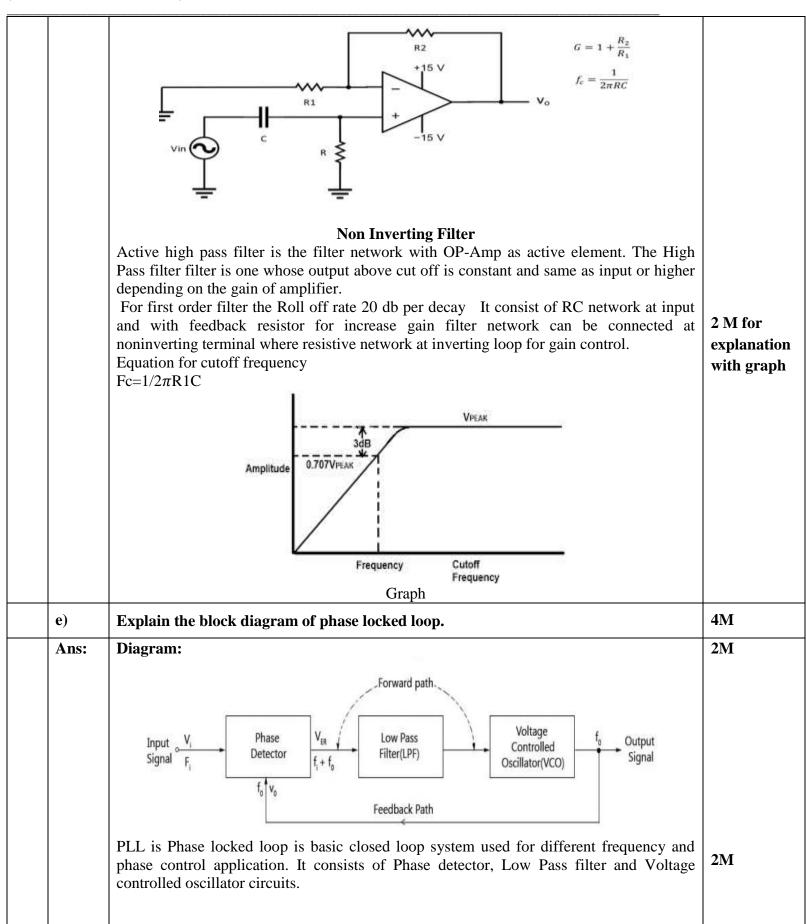

|     |      | Phase Detector:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|     |      | The input signal 'Vi' with an input frequency 'Fi' is conceded by a phase detector. Basically the phase detector is a comparator that compares the input frequency fi through the feedback frequency fo. The output of the phase detector is (fi+fo) which is a DC voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |

|     |      | Low Pass Filter:  The out of the phase detector, i.e., DC voltage is input to the low pass filter (LPF); it removes the high-frequency noise and produces a steady DC level, i.e., Fi-Fo. The Vf is also a dynamic characteristic of the PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                       |

|     |      | VCO: The output of the low pass filter, i.e., DC level is passed on to the VCO. The input signal is directly proportional to the output frequency of the VCO (fo). The input and output frequencies are compared and adjusted through the feedback loop until the output frequency is equal to the input frequency. Hence, the PLL works like free running, capture, and phase lock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                       |

| Q.5 |      | Attempt any TWO of the following                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12<br>Total Marks     |

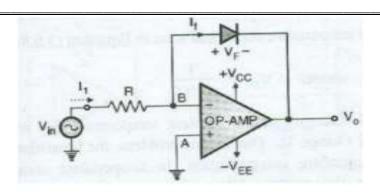

|     | (a)  | Explain the function of sample and hold circuit by using op-amp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6M                    |

|     | Ans: | Input buffer Basic sample Output buffer  HVcc  H | Circuit<br>diagram-3M |

|     |      | The n-channel MOSFET is driven by a control voltage VC acts as a switch. The control voltage VC is applied to the gate of the MOSFET. The circuit diagram can be split into three stages. First stage is the voltage follower second one is the switch and capacitor and the third one is a gain the voltage follower. When VC is high the MOSFET turns on and acts like a closed switch .This is sampling mode .The capacitor charges through the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Explanation - 3M      |